xzxb

所在地区:

全国

首页

服务/硬件产品

行业解决方案

案例

方案概述:

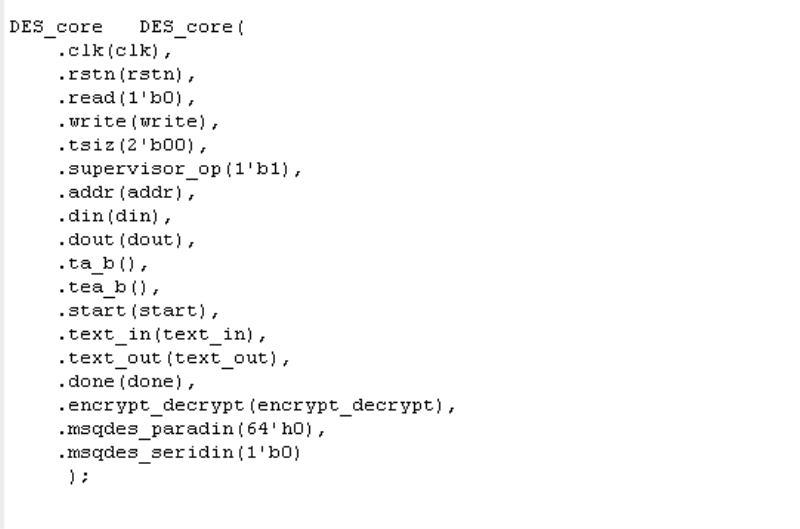

我们提供基于VERILOG设计的DES 3DES IP算法源码,具有高效、安全的加密解密操作。采用防DPA措施,有效防止侧信道攻击。支持软件3DES加速,提高加密速度。完成1次DES运算仅需16个cycle,在保证安全性的同时提供高运算效率。提供32位SFR接口和64位数据接口,方便数据交互和处理大容量数据。稳定的工作状态和可靠性保证。密钥填入方式与数据相同,保证密钥安全。实现高效、安全的加密解密算法,保护敏感数据的安全性。

我们提供基于VERILOG设计的DES 3DES IP算法源码,该解决方案具有以下特点和功能:

1) 支持数据的ECB模式加(解)密,可以对数据进行高效的加密和解密操作。

2) 采用了防DPA措施,包括随机等待、随机数掩码和数字功耗补偿等,可以有效防止侧信道攻击。

3) 支持软件3DES加速,不需要读出中间结果,可以直接进行下一轮运算,提高了加密速度。

4) 完成1次DES运算仅需16个cycle(不开启随机等待措施),在保证安全性的同时,也提供了较高的运算效率。

5) 提供了32位SFR接口,支持8/16/32 bit操作,方便与其他系统进行数据交互。

6) 提供了64位数据接口,可以处理大容量的数据。

7) 所有寄存器采用时钟上升沿有效,复位低有效,复位沿离时钟有效沿需隔半个时钟周期,确保了稳定的工作状态。

8) DES模块与CPU需要在相同的时钟域下工作,内部未对时钟或复位信号做任何处理,未对任何数据信号作同步处理,保证了系统的稳定性和可靠性。

9) 密钥填入方式与数据相同,均为从高位到低位填入,并且密钥寄存器读出值始终为0,确保了密钥的安全性。

通过使用我们提供的DES 3DES IP算法源码,您可以在工业领域中实现高效、安全的加密解密算法,保护敏感数据的安全性。

1) 支持数据的ECB模式加(解)密,可以对数据进行高效的加密和解密操作。

2) 采用了防DPA措施,包括随机等待、随机数掩码和数字功耗补偿等,可以有效防止侧信道攻击。

3) 支持软件3DES加速,不需要读出中间结果,可以直接进行下一轮运算,提高了加密速度。

4) 完成1次DES运算仅需16个cycle(不开启随机等待措施),在保证安全性的同时,也提供了较高的运算效率。

5) 提供了32位SFR接口,支持8/16/32 bit操作,方便与其他系统进行数据交互。

6) 提供了64位数据接口,可以处理大容量的数据。

7) 所有寄存器采用时钟上升沿有效,复位低有效,复位沿离时钟有效沿需隔半个时钟周期,确保了稳定的工作状态。

8) DES模块与CPU需要在相同的时钟域下工作,内部未对时钟或复位信号做任何处理,未对任何数据信号作同步处理,保证了系统的稳定性和可靠性。

9) 密钥填入方式与数据相同,均为从高位到低位填入,并且密钥寄存器读出值始终为0,确保了密钥的安全性。

通过使用我们提供的DES 3DES IP算法源码,您可以在工业领域中实现高效、安全的加密解密算法,保护敏感数据的安全性。

为您推荐其他供应商的行业解决方案

免责声明:本网站部分内容来源互联网,如权利人发现存在侵权信息,请及时与本站联系删除。

供应商:

xzxb

所在区域: 全国

xzxb是一家专注于电路设计方案和硬件开发的公司。我们擅长于提供各种电路设计方案,包括单片机、FPGA、DSP等领域的开发板和核心板设计。我们的产品涵盖了Xilinx FPGA、51单片机、以太网、蓝牙控制、USB 3.0控制芯片、智能家居等多个领域。我们提供完整的解决方案,包括电路图及BOM、仿真器源码、远程监控等。我们还提供Altium Designer、Protel等软件的元件库、封装库和原理图库,方便客户进行设计和开发。我们的团队拥有多年的工作经验和丰富的技术积累,能够为客户提供高质量的产品和解决方案。我们的目标是为客户提供最优秀的电路设计和硬件开发服务,帮助客户实现他们的创新想法。